# How to quickly deploy a SoC on FPGA to evaluate security solutions for communicating embedded systems?

International Winter School on Microarchitectural Security 2022

Philippe TANGUY December 06, 2022

Lab-STICC

### Objectives:

Explained our needs and requirements related to our research topic

### Objectives:

- Explained our needs and requirements related to our research topic

- ► Present a tool to generate a System-On-Chip quickly for FPGA : RFTX about LiteX

### Objectives:

- ► Explained our needs and requirements related to our research topic

- ► Present a tool to generate a System-On-Chip quickly for FPGA : RFTX about LiteX

- ► Introduce our hands-on: introducte LiTeX and how it could be usefull for security evaluation of embedded system software/hardware counter measures.

## Problems Statements and Requirements

► An embedded systems involves skills at the hadware level and software level

- ► An embedded systems involves skills at the hadware level and software level

- ▶ Developping for an embedded system needs to manage several tools: toolchain, several language, scripting, debug tools, JTAG, ...

- ► An embedded systems involves skills at the hadware level and software level

- ▶ Developping for an embedded system needs to manage several tools: toolchain, several language, scripting, debug tools, JTAG, ...

- ► How to go from idea to proof-of-concept quickly : for demonstration, etc.

- ► An embedded systems involves skills at the hadware level and software level

- ► Developping for an embedded system needs to manage several tools: toolchain, several language, scripting, debug tools, JTAG, ...

- ► How to go from idea to proof-of-concept quickly : for demonstration, etc.

- ► A PhD thesis is only 3 years (in France)

- ► An embedded systems involves skills at the hadware level and software level

- ► Developping for an embedded system needs to manage several tools: toolchain, several language, scripting, debug tools, JTAG, ...

- How to go from idea to proof-of-concept quickly: for demonstration, etc.

- ► A PhD thesis is only 3 years (in France)

- ► How to manage research artifacts certified as reproducible

### **Specific Problems Statements**

► At the hardware level a System On Chip can be complex and at some point we contribute to a specific part of the overall system

### **Specific Problems Statements**

- ► At the hardware level a System On Chip can be complex and at some point we contribute to a specific part of the overall system

- ► Hardware description language

► Open source tools as much as possible

- ► Open source tools as much as possible

- ► Benefits of community

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Build automation

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Build automation

- ► Support several FPGA, devkit boards, ...

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Build automation

- ► Support several FPGA, devkit boards, ...

- Make comparison of several implementation without developping everything from scratch

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Build automation

- ► Support several FPGA, devkit boards, ...

- ► Make comparison of several implementation without developping everything from scratch

- ► Have examples or support about deploying RTOS OS and/or Linux

- ► Open source tools as much as possible

- ► Benefits of community

- ► Do not reinvent the wheel

- ► Build automation

- ► Support several FPGA, devkit boards, ...

- ► Make comparison of several implementation without developping everything from scratch

- ► Have examples or support about deploying RTOS OS and/or Linux

Which tool to use?

We choose to use LiteX!

Quick demo!

FPGA 101 (in 5min)

### ASIC et programmable circuit

### **Terminology**

- ► ASIC : Application-specific integrated circuit

- ► PLD : Programmable Logic Device

### ASIC vs PLD

- ▶ VHDL (or Verilog, ...) allows to descibes hardware for ASIC or PLD

- ► ASIC are dedicted component

- ► PLD are programmable component

### Au commencement ...

Microprocessor and FPGA are dedicated component.

- ► First microprocessor (1971)

- ► Allows to execute intruction and process program data

- First FPGA (field programmable gate array) (1985)

- Allows to define a circuit to realize a function (Xor, FFT, CPU

| Niveau       | Microprocessorr | FPGA |

|--------------|-----------------|------|

| Transistor   |                 |      |

| Logic        | Arch. fixed     |      |

| Architecture | μp              |      |

| Algorithm    |                 |      |

| Niveau       | Microprocessorr | FPGA |

|--------------|-----------------|------|

| Transistor   |                 |      |

| Logic        | Arch. fixed     |      |

| Architecture | μρ              |      |

| Algorithm    | Soft for CPU    |      |

| Niveau       | Microprocessorr | FPGA        |

|--------------|-----------------|-------------|

| Transistor   |                 | Arch. fixed |

| Logic        | Arch. fixed     |             |

| Architecture | μρ              |             |

| Algorithm    | Soft for CPU    |             |

| Niveau       | Microprocessorr | FPGA        |

|--------------|-----------------|-------------|

| Transistor   |                 | Arch. fixed |

| Logic        | Arch. fixed     | Netlist     |

| Architecture | μρ              | (HDL prog.) |

| Algorithm    | Soft for CPU    | Soft SoC    |

### Overview

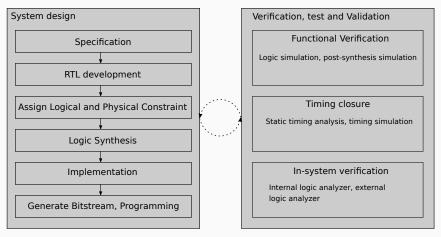

Example on the demo with Vivado!

### LiteX 101

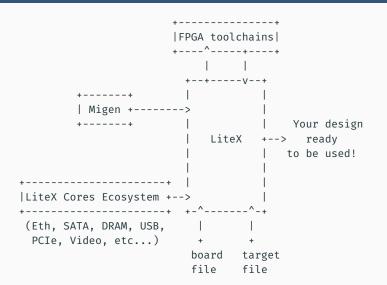

### LiteX?

Img Credits : LiteX

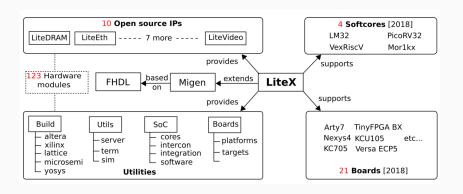

### LiteX and component?

Img credits: https://pcotret.github.io/ENSTAB-RISCV/

### LiteX Hub: LiteX-boards

Support a lot of FPGA chip, boards and dev kit!

```

(pyenv-litex)> ls litex-boards/litex boards/targets/

1

zsh: do you wish to see all 132 possibilities (66 lines)?

2

(pyenv-litex)> ls -l litex-boards/litex boards/targets/digilent *

3

litex-boards/litex boards/targets/digilent arty.py

4

litex-boards/litex boards/targets/digilent basys3.py

5

litex-boards/litex boards/targets/digilent nexys4.py

6

litex-boards/litex boards/targets/digilent arty s7.pv

litex-boards/litex_boards/targets/digilent_cmod_a7.py

8

litex-boards/litex boards/targets/digilent nexys video.py

9

litex-boards/litex boards/targets/digilent arty z7.py

10

litex-boards/litex_boards/targets/digilent_genesys2.py

11

litex-boards/litex_boards/targets/digilent_pynq_z1.py

12

litex-boards/litex boards/targets/digilent atlys.py

13

litex-boards/litex boards/targets/digilent nexys4ddr.py

14

litex-boards/litex_boards/targets/digilent_zedboard.py

15

```

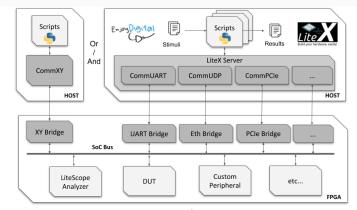

### LiteX debug infrastructure

LiteX Remote Control/Debug Infrastructure

Img credits : LiTeX Github

### Interesting project/paper using LiteX i

► LiteX embench tester https://github.com/antmicro/embench-tester

Img credits: antmicro

### Interesting project/paper using LiteX ii

► LiteX rowhammer tester https://github.com/antmicro/rowhammer-tester

14/16

Conclusion

### Conclusion about LiteX

- ► Usefull for constraint embedded system : simple SoC, simple Core, ...

- ▶ It is not an industrial framework but it works ...

### Hands-on overview

- ► Labs available online https://sourcesup.renater.fr/www/mic-sec-2022/

- ▶ 3 labs:

- ► Lab 01 : Getting Started with LiteX

- ► Lab 02 : Create a minimal SoC with LiTeX

- ► Lab 03 : Software app for a SoC with LiTeX

Questions/Discussions?

(Hands-on after the break!)

### Acknowledgements

- ► LiteX community

- ► Thesis Mohamed El-bouazzati